# Features

- 8-bit Microcontroller Compatible with MCS<sup>®</sup>51 Products

- Enhanced 8051 Architecture

- Single Clock Cycle per Byte Fetch

- Up to 20 MIPS Throughput at 20 MHz Clock Frequency

- Fully Static Operation: 0 Hz to 20 MHz

- On-chip 2-cycle Hardware Multiplier

- 128 x 8 Internal RAM

- 4-level Interrupt Priority

- Nonvolatile Program Memory

- 2K Bytes of In-System Programmable (ISP) Flash Memory

- Endurance: Minimum 10,000 Write/Erase Cycles

- Serial Interface for Program Downloading

- 32-byte Fast Page Programming Mode

- 64-byte User Signature Array

- 2-level Program Memory Lock for Software Security

- Peripheral Features

- Two 16-bit Enhanced Timer/Counters

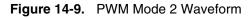

- Two 8-bit PWM Outputs (AT89LP213 Only)

- Enhanced UART with Automatic Address Recognition and Framing Error Detection (AT89LP214 Only)

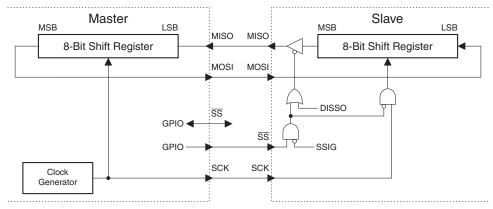

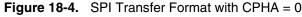

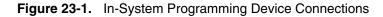

- Enhanced Master/Slave SPI with Double-buffered Send/Receive

- Programmable Watchdog Timer with Software Reset

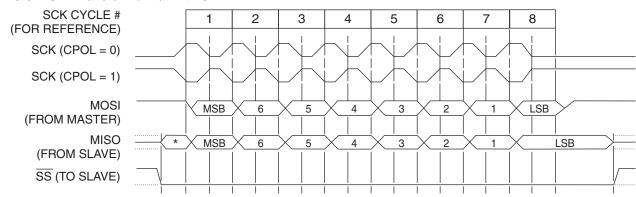

- Analog Comparator with Selectable Interrupt and Debouncing

- 8 General-purpose Interrupt Pins

- Special Microcontroller Features

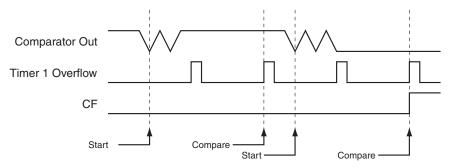

- Two-wire On-chip Debug Interface

- Brown-out Detection and Power-on Reset with Power-off Flag

- Internal 8 MHz RC Oscillator

- Low Power Idle and Power-down Modes

- Interrupt Recovery from Power-down Mode

- I/O and Packages

- Up to 12 Programmable I/O Lines

- Configurable I/O with Quasi-bidirectional, Input, Push-pull Output, and Open-drain Modes

- 5V Tolerant I/O

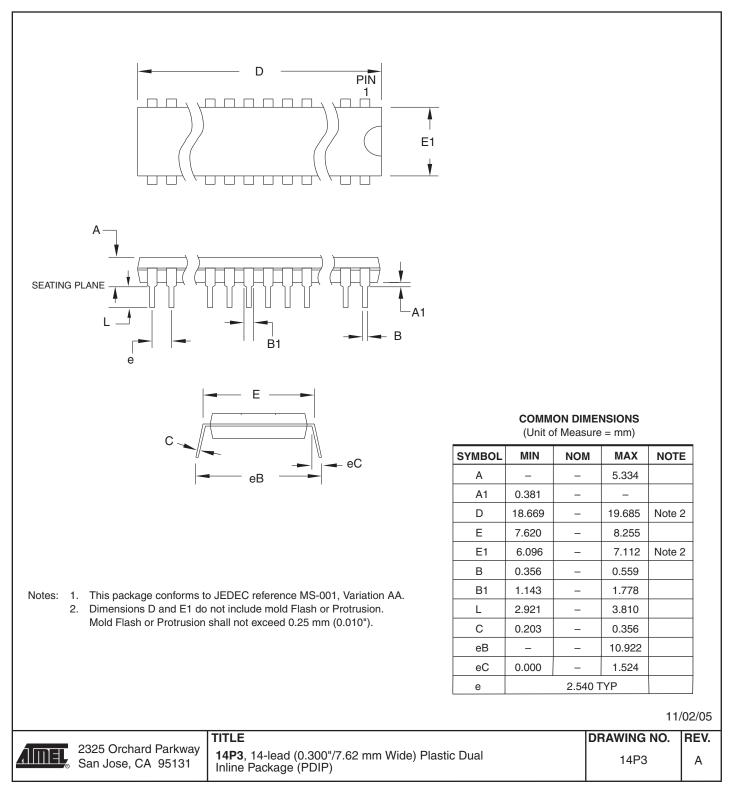

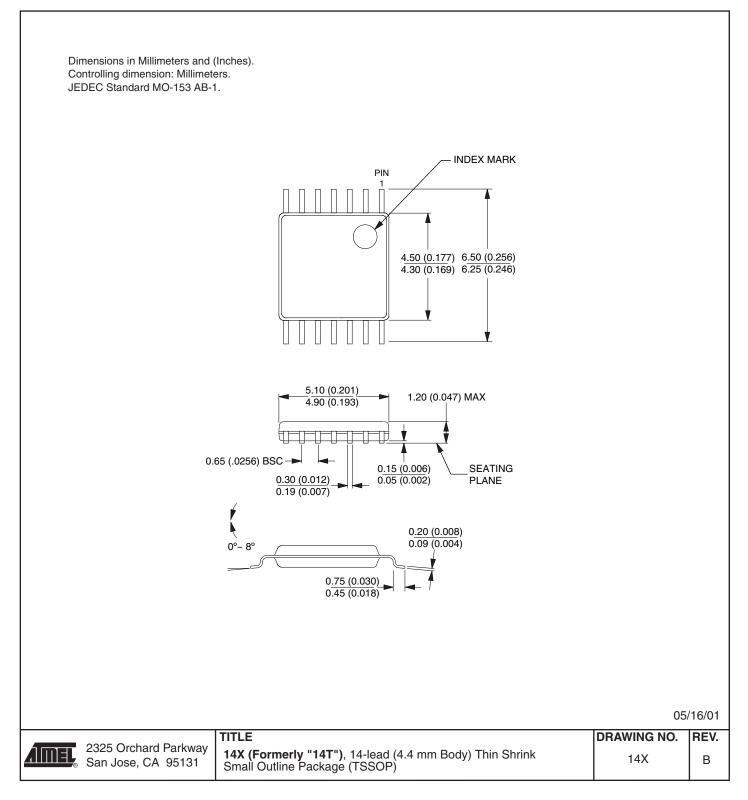

- 14-lead TSSOP or PDIP

- Operating Conditions

- 2.4V to 5.5V V<sub>CC</sub> Voltage Range

- 40° C to 85°C Temperature Range

# 1. Description

The AT89LP213/214 is a low-power, high-performance CMOS 8-bit microcontroller with 2K bytes of In-System Programmable Flash memory. The device is manufactured using Atmel's high-density nonvolatile memory technology and is compatible with the industry-standard MCS-51 instruction set. The AT89LP213/214 is built around an enhanced CPU core that can fetch a single byte from memory every clock cycle. In the classic 8051 architecture, each fetch requires 6 clock cycles, forcing instructions to execute in 12, 24 or 48 clock cycles. In the AT89LP213/214 CPU, instructions

8-bit Microcontroller with 2K Bytes Flash

AT89LP213 AT89LP214

3538C-MICRO-06/08

need only 1 to 4 clock cycles providing 6 to 12 times more throughput than the standard 8051. Seventy percent of instructions need only as many clock cycles as they have bytes to execute, and most of the remaining instructions require only one additional clock. The enhanced CPU core is capable of 20 MIPS throughput whereas the classic 8051 CPU can deliver only 4 MIPS at the same current consumption. Conversely, at the same throughput as the classic 8051, the new CPU core runs at a much lower speed and thereby greatly reduces power consumption.

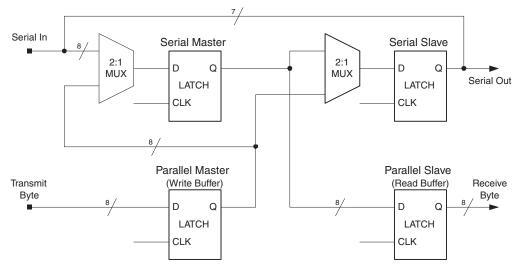

The AT89LP213/214 provides the following standard features: 2K bytes of In-System Programmable Flash memory, 128 bytes of RAM, up to 12 I/O lines, two 16-bit timer/counters, two PWM outputs (AT89LP213 only), a programmable watchdog timer, a full duplex serial port (AT89LP214 only), a serial peripheral interface, an internal 8 MHz RC oscillator, on-chip crystal oscillator, and a four-level, six-vector interrupt system.

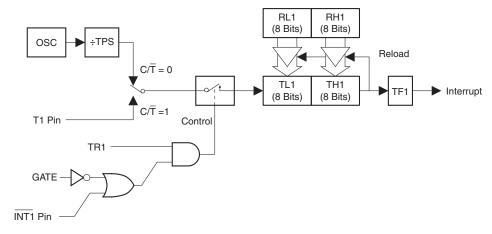

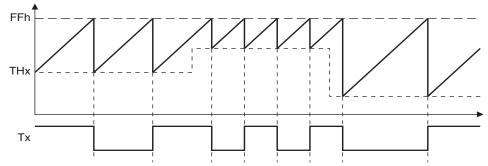

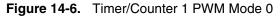

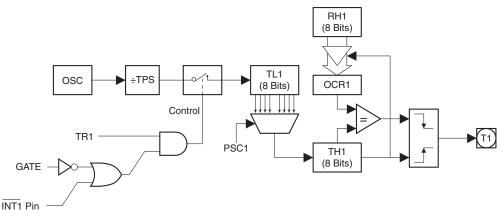

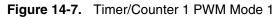

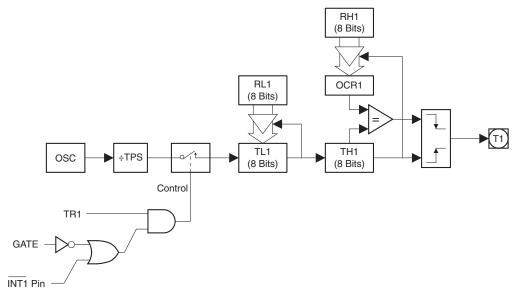

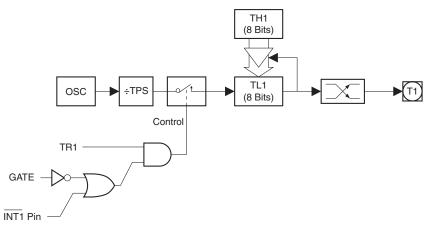

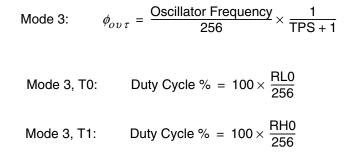

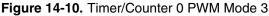

The two timer/counters in the AT89LP213/214 are enhanced with two new modes. Mode 0 can be configured as a variable 9- to 16-bit timer/counter and Mode 1 can be configured as a 16-bit auto-reload timer/counter. In addition, the timer/counters on the AT89LP213 may independently drive a pulse width modulation output.

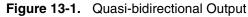

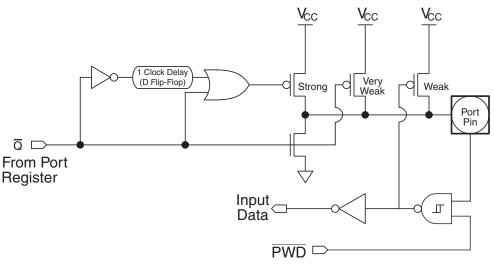

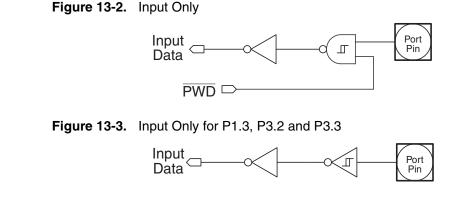

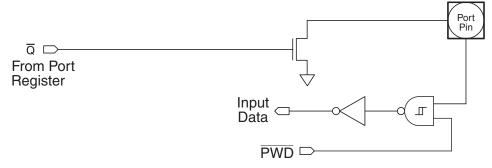

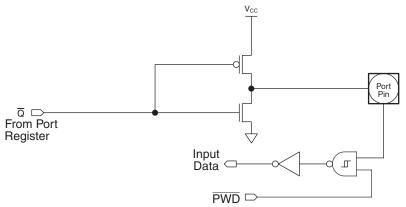

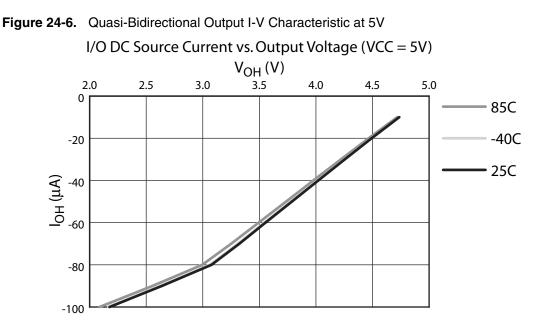

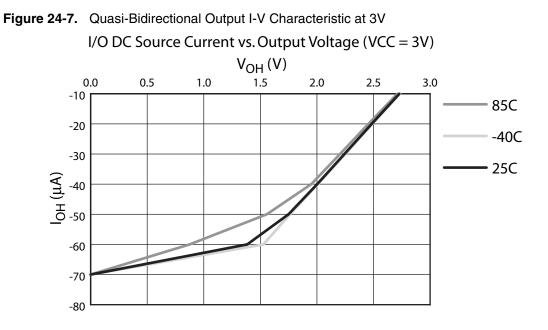

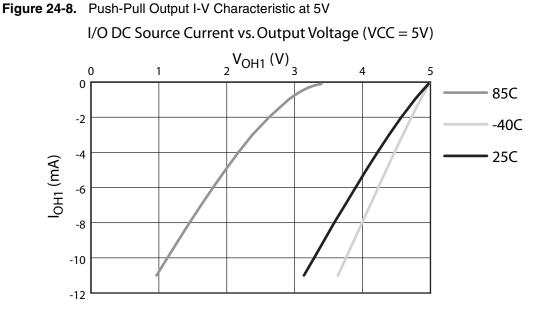

The I/O ports of the AT89LP213/214 can be independently configured in one of four operating modes. In quasi-bidirectional mode, the ports operate as in the classic 8051. In input mode, the ports are tristated. Push-pull output mode provides full CMOS drivers and open-drain mode provides just a pull-down. In addition, all 8 pins of Port 1 can be configured to generate an interrupt using the general-purpose interrupt interface. The I/O pins of the AT89LP213/214 tolerate voltages higher than the device's own power supply, up to 5.5V. When the device is supplied at 2.4V and all I/O ports receive 5.5V, the total back flowing current in all I/Os is less than 100  $\mu$ A.

# 2. Pin Configuration

2.2

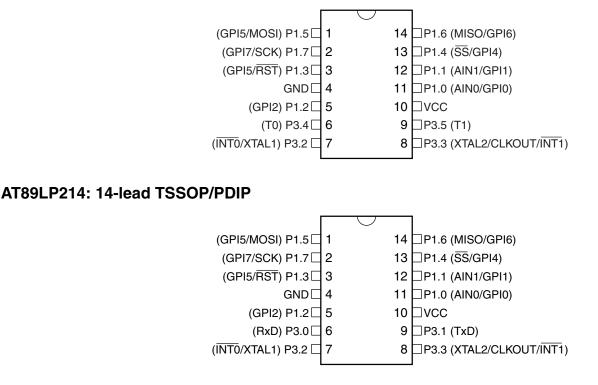

# 2.1 AT89LP213: 14-lead TSSOP/PDIP

# <sup>2</sup> AT89LP213/214

# 3. Pin Description

Table 3-1.AT89LP213 Pin Description

| Pin | Symbol | Туре               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----|--------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

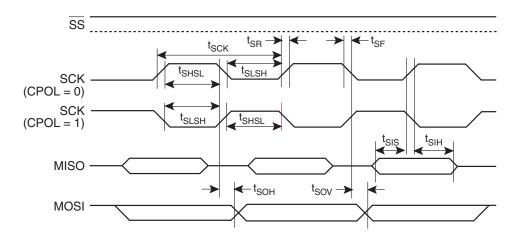

| 1   | P1.5   | I/O<br>I/O<br>I    | <ul> <li>P1.5: User-configurable I/O Port 1 bit 5.</li> <li>MOSI: SPI master-out/slave-in. When configured as master, this pin is an output. When configured as slave, this pin is an input.</li> <li>GPI5: General-purpose Interrupt input 5.</li> </ul>                                                                                                                                                                                                                                                     |

| 2   | P1.7   | I/O<br>I/O<br>I    | <ul> <li>P1.7: User-configurable I/O Port 1 bit 7.</li> <li>SCK: SPI Clock. When configured as master, this pin is an output. When configured as slave, this pin is an input.</li> <li>GPI7: General-purpose Interrupt input 7.</li> </ul>                                                                                                                                                                                                                                                                    |

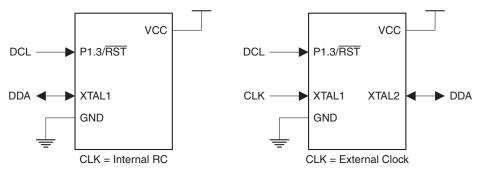

| 3   | P1.3   | I/O<br>I<br>I<br>I | <ul> <li>P1.3: User-configurable I/O Port 1 bit 3 (if Reset Fuse is disabled).</li> <li>RST: External Active-Low Reset input (if Reset Fuse is enabled. See "External Reset" on page 16).</li> <li>GPI3: General-purpose Interrupt input 3.</li> <li>DCL: Serial Clock input for On-chip Debug Interface when OCD is enabled.</li> </ul>                                                                                                                                                                      |

| 4   | GND    | I                  | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5   | P1.2   | I/O<br>I           | P1.2: User-configurable I/O Port 1 bit 2.<br>GPI2: General-purpose Interrupt input 2.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 6   | P3.4   | I/O<br>I/O         | <b>P3.4</b> : User-configurable I/O Port 3 bit 4.<br><b>T0</b> : Timer/Counter 0 External Input or PWM Output.                                                                                                                                                                                                                                                                                                                                                                                                |

| 7   | P3.2   | I/O<br>I<br>I/O    | <ul> <li>P3.2: User-configurable I/O Port 3 bit 2.</li> <li>XTAL1: Input to the inverting oscillator amplifier and internal clock generation circuits. It may be used as a port pin if the internal RC oscillator is selected as the clock source.</li> <li>DDA: Serial Data input/output for On-chip Debug Interface when OCD is enabled and the internal RC oscillator is selected as the clock source.</li> </ul>                                                                                          |

| 8   | P3.3   | I/O<br>O<br>I/O    | <ul> <li>P3.3: User-configurable I/O Port 3 bit 3.</li> <li>XTAL2: Output from inverting oscillator amplifier. It may be used as a port pin if the internal RC oscillator is selected as the clock source.</li> <li>CLKOUT: When the internal RC oscillator is selected as the clock source, may be used to output the internal clock divided by 2.</li> <li>DDA: Serial Data input/output for On-chip Debug Interface when OCD is enabled and the external clock is selected as the clock source.</li> </ul> |

| 9   | P3.5   | I/O<br>I/O         | P3.5: User-configurable I/O Port 3 bit 5.<br>T1: Timer/Counter 1 External input or PWM output.                                                                                                                                                                                                                                                                                                                                                                                                                |

| 10  | VCC    | I                  | Supply Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 11  | P1.0   | I/O<br>I<br>I      | P1.0: User-configurable I/O Port 1 bit 0.<br>AIN0: Analog Comparator Positive input.<br>GPI0: General-purpose Interrupt input 0.                                                                                                                                                                                                                                                                                                                                                                              |

| 12  | P1.1   | I/O<br>I<br>I      | P1.1: User-configurable I/O Port 1 bit 1.<br>AIN1: Analog Comparator Negative input.<br>GPI1: General-purpose Interrupt input 1                                                                                                                                                                                                                                                                                                                                                                               |

| 13  | P1.4   | I/O<br>I<br>I      | P1.4: User-configurable I/O Port 1 bit 4.<br>SS: SPI slave select input.<br>GPI4: General-purpose Interrupt input 4.                                                                                                                                                                                                                                                                                                                                                                                          |

| 14  | P1.6   | I/O<br>I/O<br>I    | <ul> <li>P1.6: User-configurable I/O Port 1 bit 6.</li> <li>MISO: SPI master-in/slave-out. When configured as master, this pin is an input. When configured as slave, this pin is an output.</li> <li>GPI6: General-purpose Interrupt input 6.</li> </ul>                                                                                                                                                                                                                                                     |

### Table 3-2.AT89LP214 Pin Description

| Pin | Symbol | Туре            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|--------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | P1.5   | I/O<br>I/O      | <b>P1.5</b> : User-configurable I/O Port 1 bit 5.<br><b>MOSI</b> : SPI master-out/slave-in. When configured as master, this pin is an output. When configured as slave, this pin is an input.<br><b>GPI5</b> : General-purpose Interrupt input 5.                                                                                                                                                                                                                                                              |

| 2   | P1.7   | I/O<br>I/O<br>I | <ul> <li>P1.7: User-configurable I/O Port 1 bit 7.</li> <li>SCK: SPI Clock. When configured as master, this pin is an output. When configured as slave, this pin is an input.</li> <li>GPI7: General-purpose Interrupt input 7.</li> </ul>                                                                                                                                                                                                                                                                     |

| 3   | P1.3   | I/O<br>I<br>I   | <ul> <li>P1.3: User-configurable I/O Port 1 bit 3 (if Reset Fuse is disabled).</li> <li>RST: External Active-Low Reset input (if Reset Fuse is enabled. See "External Reset" on page 16).</li> <li>GPI3: General-purpose Interrupt input 3.</li> <li>DCL: Serial Clock input for On-chip Debug Interface.</li> </ul>                                                                                                                                                                                           |

| 4   | GND    | I               | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5   | P1.2   | I/O<br>I        | P1.2: User-configurable I/O Port 1 bit 2.<br>GPI2: General-purpose Interrupt input 2.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 6   | P3.0   | I/O<br>I        | P3.0: User-configurable I/O Port 3 bit 0.<br>RXD: Serial Port Receiver input.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |        | I/O<br>I        | <b>P3.2</b> : User-configurable I/O Port 3 bit 2.<br><b>XTAL1</b> : Input to the inverting oscillator amplifier and internal clock generation circuits. It may be used as                                                                                                                                                                                                                                                                                                                                      |

| 7   | P3.2   | I/O             | a port pin if the internal RC oscillator is selected as the clock source.<br><b>DDA</b> : Serial Data input/output for On-chip Debug Interface when OCD is enabled and the internal RC oscillator is selected as the clock source.                                                                                                                                                                                                                                                                             |

| 8   | P3.3   | I/O<br>O<br>I/O | <ul> <li>P3.3: User-configurable I/O Port 3 bit 3.</li> <li>XTAL2: Output from inverting oscillator amplifier. It may be used as a port pin if the internal RC oscillator is selected as the clock source.</li> <li>CLKOUT: When the internal RC oscillator is selected as the clock source, may be used to output the internal clock divided by 2.</li> <li>DDA: Serial Data input/output for On-chip Debug Interface when OCD is enabled and the external clock is selected as the clock source.\</li> </ul> |

| 9   | P3.1   | I/O<br>O        | P3.1: User-configurable I/O Port 3 bit 1.<br>TXD: Serial Port Transmitter output.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 10  | VCC    | I               | Supply Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 11  | P1.0   | I/O<br>I<br>I   | P1.0: User-configurable I/O Port 1 bit 0.<br>AIN0: Analog Comparator Positive input.<br>GPI0: General-purpose Interrupt input 0.                                                                                                                                                                                                                                                                                                                                                                               |

| 12  | P1.1   | I/O<br>I<br>I   | P1.1: User-configurable I/O Port 1 bit 1.<br>AIN1: Analog Comparator Negative input.<br>GPI1: General-purpose Interrupt input 1                                                                                                                                                                                                                                                                                                                                                                                |

| 13  | P1.4   | I/O<br>I<br>I   | P1.4: User-configurable I/O Port 1 bit 4.<br>SS: SPI slave select input.<br>GPI4: General-purpose Interrupt input 4.                                                                                                                                                                                                                                                                                                                                                                                           |

| 14  | P1.6   | I/O<br>I/O<br>I | <ul> <li>P1.6: User-configurable I/O Port 1 bit 6.</li> <li>MISO: SPI master-in/slave-out. When configured as master, this pin is an input. When configured as slave, this pin is an output.</li> <li>GPI6: General-purpose Interrupt input 6.</li> </ul>                                                                                                                                                                                                                                                      |

# 4. Block Diagram

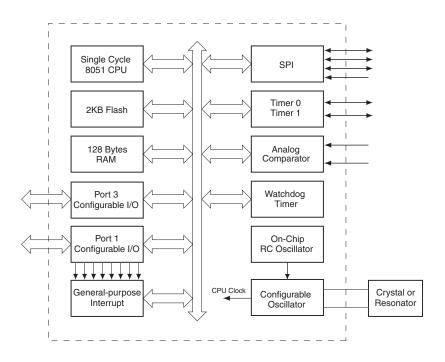

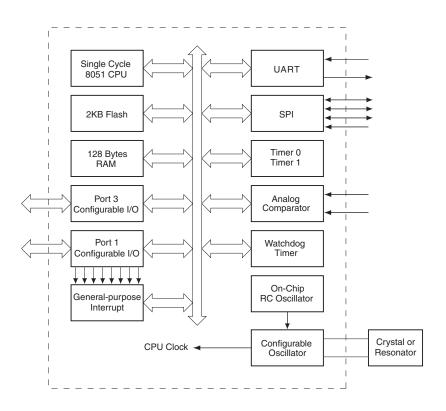

Figure 4-1. AT89LP213 Block Diagram

# 5. Comparison to Standard 8051

The AT89LP213/214 is part of a family of devices with enhanced features that are fully binary compatible with the MCS-51 instruction set. In addition, most SFR addresses, bit assignments, and pin alternate functions are identical to Atmel's existing standard 8051 products. However, due to the high performance nature of the device, some system behaviors are different from those of Atmel's standard 8051 products such as AT89S52 or AT89S2051. The differences from the standard 8051 are outlined in the following paragraphs.

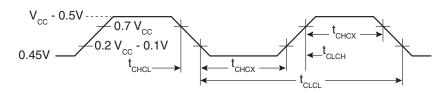

### 5.1 System Clock

The CPU clock frequency equals the external XTAL1 frequency. The oscillator is no longer divided by 2 to provide the internal clock and x2 mode is not supported.

# 5.2 Instruction Execution with Single-cycle Fetch

The CPU fetches one code byte from memory every clock cycle instead of every six clock cycles. This greatly increases the throughput of the CPU. As a consequence, the CPU no longer executes instructions in 12 to 48 clock cycles. Each instruction executes in only 1 to 4 clock cycles. See "Instruction Set Summary" on page 60 for more details.

# 5.3 Interrupt Handling

The interrupt controller polls the interrupt flags during the last clock cycle of any instruction. In order for an interrupt to be serviced at the end of an instruction, its flag needs to have been latched as active during the next to last clock cycle of the instruction, or in the last clock cycle of the previous instruction if the current instruction executes in only a single clock cycle.

The external interrupt pins, INTO and INT1, are sampled at every clock cycle instead of once every 12 clock cycles. Coupled with the shorter instruction timing and faster interrupt response, this leads to a higher maximum rate of incidence for the external interrupts.

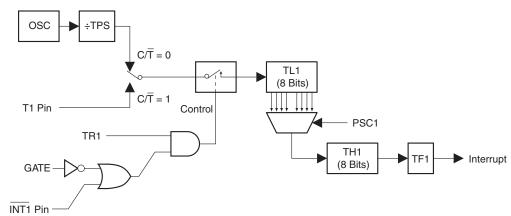

# 5.4 Timer/Counters

By default the Timer/Counters is incremented at a rate of once per clock cycle. This compares to once every 12 clocks in the standard 8051. A common prescaler is available to divide the time base for all timers and reduce the increment rate. The TPS bits in the CLKREG SFR control the prescaler (Table 9-2 on page 14). Setting TPS = 1011B will cause the timers to count once every 12 clocks.

The external Timer/Counter pins, T0 and T1, are sampled at every clock cycle instead of once every 12 clock cycles. This increases the maximum rate at which the Counter modules may function.

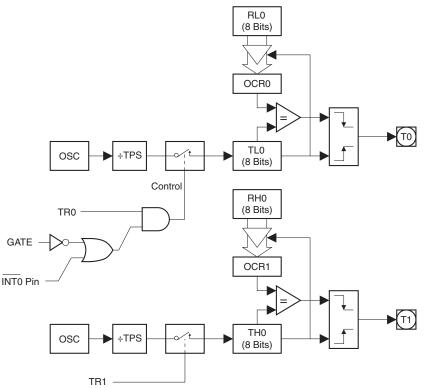

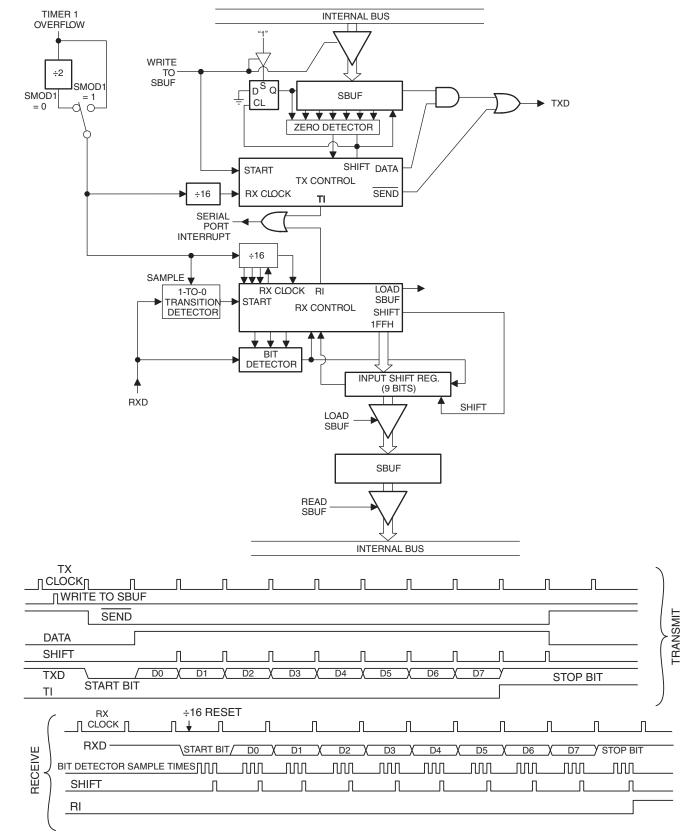

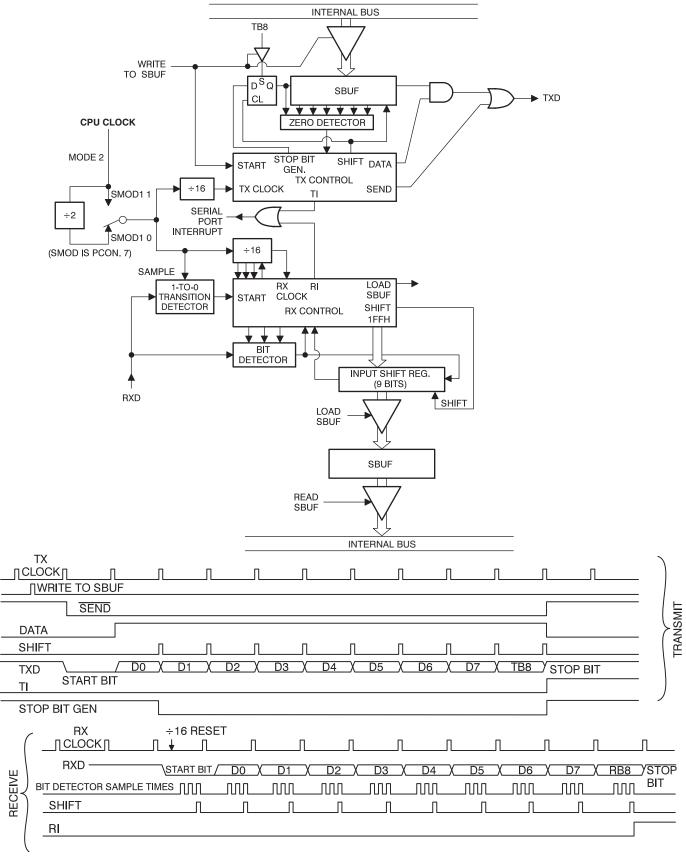

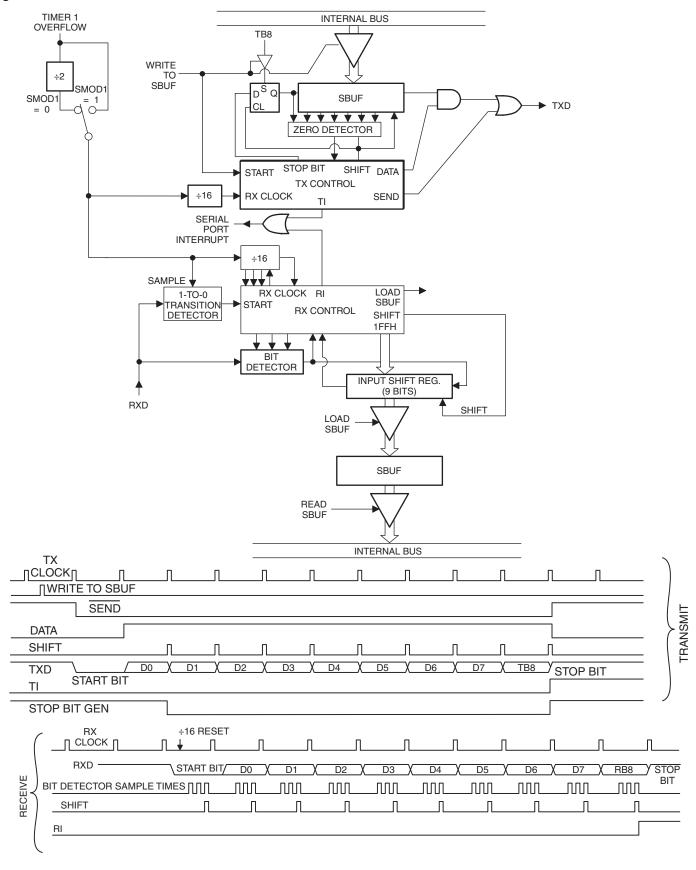

#### 5.5 Serial Port

The baud rate of the UART in Mode 0 is 1/2 the clock frequency, compared to 1/12 the clock frequency in the standard 8051; and output data is only stable around the rising edge of the serial clock. In should also be noted that when using Timer 1 to generate the baud rate in Mode 1 or Mode 3, the timer counts at the clock frequency and not at 1/12 the clock frequency. To maintain the same baud rate in the AT89LP214 while running at the same frequency as a standard 8051, the time-out period must be 12 times longer. Mode 1 of Timer 1 supports 16-bit auto-reload to facilitate longer time-out periods for generating low baud rates.

# 6 AT89LP213/214 -----

### 5.6 Watchdog Timer

The Watchdog Timer in AT89LP213/214 counts at a rate of once per clock cycle. This compares to once every 12 clocks in the standard 8051. A common prescaler is available to divide the time base for all timers and reduce the counting rate.

### 5.7 I/O Ports

The I/O ports of the AT89LP213/214 may be configured in four different modes. By default all the I/O ports revert to input-only (tristated) mode at power-up or reset. In the standard 8051, all ports are weakly pulled high during power-up or reset. To enable 8051-like ports, the ports must be put into quasi-bidirectional mode by clearing the P1M0 and P3M0 SFRs. The user can also configure the ports to start in quasi-bidirectional mode by disabling the Tristate-Port User Fuse. When this fuse is disabled, P1M0 and P3M0 will reset to 00h instead of FFh and the ports will be weakly pulled high.

#### 5.8 Reset

The  $\overline{\text{RST}}$  pin of the AT89LP213/214 is active-low as compared with the active high reset in the standard 8051. In addition, the  $\overline{\text{RST}}$  pin is sampled every clock cycle and must be held low for a minimum of two clock cycles, instead of 24 clock cycles, to be recognized as a valid reset.

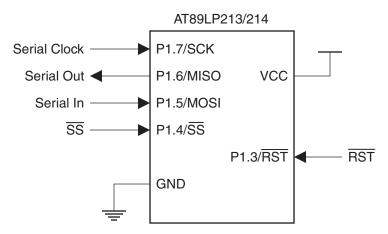

# 6. Memory Organization

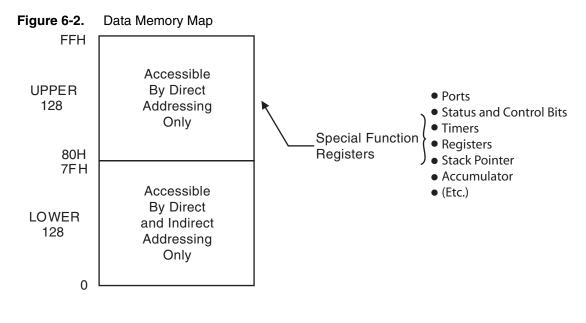

The AT89LP213/214 uses a Harvard Architecture with separate address spaces for program and data memory. The program memory has a regular linear address space with support for up to 64K bytes of directly addressable application code. The data memory has 128 bytes of internal RAM and 128 bytes of Special Function Register I/O space. The AT89LP213/214 does not support external data memory or external program memory.

#### 6.1 Program Memory

The AT89LP213/214 contains 2K bytes of on-chip In-System Programmable Flash memory for program storage. The Flash memory has an endurance of at least 10,000 write/erase cycles and a minimum data retention time of 10 years. The reset and interrupt vectors are located within the first 59 bytes of program memory (refer to Table 12-1 on page 20). Constant tables can be allocated within the entire 2K program memory address space for access by the MOVC instruction. The AT89LP213/214 does not support external program memory.

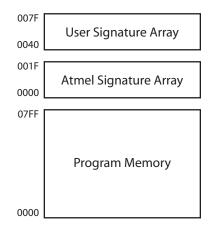

#### Figure 6-1. Program Memory Map

A map of the AT89LP213/214 program memory is shown in Figure 6-1. In addition to the 2K code space from 0000h to 07FFh, the AT89LP213/214 also supports a 64-byte User Signature Array and a 32-byte Atmel Signature Array that are accessible by the CPU in a read-only fashion. In order to read from the signature arrays, the SIGEN bit in AUXR1 must be set. While SIGEN is one, MOVC A,@A+DPTR will access the signature arrays. The User Signature Array is mapped to addresses 0040h to 007Fh and the Atmel Signature Array is mapped to addresses 0000h to 001Fh. SIGEN must be cleared before using MOVC to access the code memory.

The Atmel Signature Array is initialized with the Device ID in the factory. The User Signature Array is available for user identification codes or constant parameter data. Data stored in the signature array is not secure. Security bits will disable writes to the array; however, reads are always allowed.

Table 6-1.AUXR1 – Auxiliary Register 1

| AUX                 | AUXR1 = A2H |   |   |   |       |   | Reset Value = XXXX 0XXXB |   |  |  |

|---------------------|-------------|---|---|---|-------|---|--------------------------|---|--|--|

| Not Bit Addressable |             |   |   |   |       |   |                          |   |  |  |

|                     | _           | _ | _ | _ | SIGEN | _ | _                        | _ |  |  |

| Bit                 | 7           | 6 | 5 | 4 | 3     | 2 | 1                        | 0 |  |  |

| Bit                 | 7           | 6 | 5 | 4 | 3     | 2 | 1                        | 0 |  |  |

#### 6.2 Data Memory

The AT89LP213/214 contains 128 bytes of general SRAM data memory plus 128 bytes of I/O memory mapped into a single 8-bit address space. The 128 bytes of data memory may be accessed through both direct and indirect addressing of the lower 128 byte addresses. The 128 bytes of I/O memory reside in the upper 128 byte address space (Figure 6-2). The I/O memory can only be accessed through direct addressing and contains the Special Function Registers (SFRs). Indirect accesses to the upper 128 byte addresses will return invalid data. The lowest 32 bytes of data memory are grouped into 4 banks of 8 registers each. The RS0 and RS1 bits (PSW.3 and PSW.4) select which register bank is in use. Instructions using register addressing will only access the currently specified bank. The AT89LP213/214 does not support external data memory.

8 AT89LP213/214

# 7. Special Function Registers

A map of the on-chip memory area called the Special Function Register (SFR) space is shown in Table 7-1.

Note that not all of the addresses are occupied, and unoccupied addresses may not be implemented on the chip. Read accesses to these addresses will in general return random data, and write accesses will have an indeterminate effect. User software should not write to these unlisted locations, since they may be used in future products to invoke new features.

Table 7-1.

AT89LP213/214 SFR Map and Reset Values

|      | 8                 | 9                  | А                   | В                 | С                  | D                 | E                      | F                   |      |

|------|-------------------|--------------------|---------------------|-------------------|--------------------|-------------------|------------------------|---------------------|------|

| 0F8H |                   |                    |                     |                   |                    |                   |                        |                     | 0FFH |

| 0F0H | B<br>0000 0000    |                    |                     |                   |                    |                   |                        |                     | 0F7H |

| 0E8H | SPSR<br>000x x000 | SPCR<br>0000 0000  | SPDR<br>xxxx xxxx   |                   |                    |                   |                        |                     | 0EFH |

| 0E0H | ACC<br>0000 0000  |                    |                     |                   |                    |                   |                        |                     | 0E7H |

| 0D8H |                   |                    |                     |                   |                    |                   |                        |                     | 0DFH |

| 0D0H | PSW<br>0000 0000  |                    |                     |                   |                    |                   |                        |                     | 0D7H |

| 0C8H |                   |                    |                     |                   |                    |                   |                        |                     | 0CFH |

| 0C0H |                   |                    | P1M0 <sup>(2)</sup> | P1M1<br>xx00 0000 |                    |                   | P3M0 <sup>(2)</sup>    | P3M1<br>xx00 0000   | 0C7⊦ |

| 0B8H | IP<br>x000 0000   | SADEN<br>0000 0000 |                     |                   |                    |                   |                        |                     | 0BFH |

| 0B0H | P3<br>xx11 1111   |                    |                     |                   |                    |                   |                        | IPH<br>x000 0000    | 0B7H |

| 0A8H | IE<br>0000 0000   | SADDR<br>0000 0000 |                     |                   |                    |                   |                        |                     | 0AFH |

| 0A0H |                   |                    | AUXR1<br>xxxx 0xxx  |                   |                    |                   | WDTRST<br>(write-only) | WDTCON<br>0000 x000 | 0A7H |

| 98H  | SCON<br>0000 0000 | SBUF<br>xxxx xxxx  | GPMOD<br>0000 0000  | GPLS<br>0000 0000 | GPIEN<br>0000 0000 | GPIF<br>0000 0000 |                        |                     | 9FH  |

| 90H  | P1<br>1111 1111   | TCONB<br>0010 0100 | RL0<br>0000 0000    | RL1<br>0000 0000  | RH0<br>0000 0000   | RH1<br>0000 0000  |                        | ACSR<br>xx00 0000   | 97H  |

| 88H  | TCON<br>0000 0000 | TMOD<br>0000 0000  | TL0<br>0000 0000    | TL1<br>0000 0000  | TH0<br>0000 0000   | TH1<br>0000 0000  |                        | CLKREG<br>0000 x000 | 8FH  |

| 80H  |                   | SP<br>0000 0111    | DPL<br>0000 0000    | DPH<br>0000 0000  |                    |                   |                        | PCON<br>0000 0000   | 87H  |

|      | 0                 | 1                  | 2                   | 3                 | 4                  | 5                 | 6                      | 7                   | 1    |

Notes: 1. All SFRs in the left-most column are bit-addressable.

2. Reset value is xx11 1111B when Tristate-Port Fuse is enabled and xx00 0000B when disabled.

# 8. Enhanced CPU

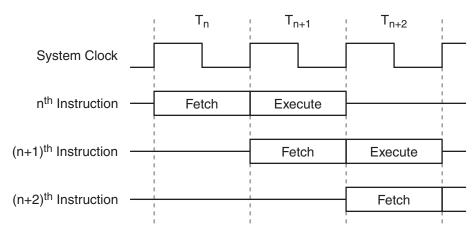

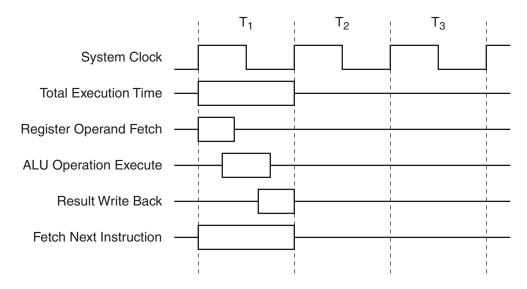

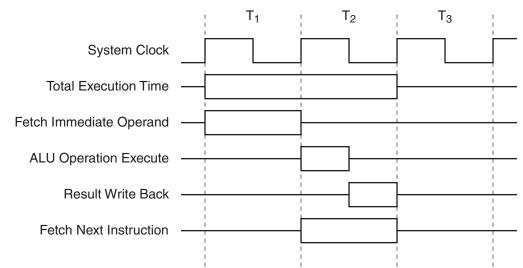

The AT89LP213/214 uses an enhanced 8051 CPU that runs at 6 to 12 times the speed of standard 8051 devices (or 3 to 6 times the speed of X2 8051 devices). The increase in performance is due to two factors. First, the CPU fetches one instruction byte from the code memory every clock cycle. Second, the CPU uses a simple two-stage pipeline to fetch and execute instructions in parallel. This basic pipelining concept allows the CPU to obtain up to 1 MIPS per MHz. A simple example is shown in Figure 8-1.

The MCS-51 instruction set allows for instructions of variable length from 1 to 3 bytes. In a single-clock-per-byte-fetch system this means each instruction takes at least as many clocks as it has bytes to execute. The majority of instructions in the AT89LP213/214 follow this rule: the instruction execution time in clock cycles equals the number of bytes per instruction with a few exceptions. Branches and Calls require an additional cycle to compute the target address and some other complex instructions require multiple cycles. See "Instruction Set Summary" on page 60 for more detailed information on individual instructions. Figures 8-2 and 8-3 show examples of 1- and 2-byte instructions.

# Figure 8-1. Parallel Instruction Fetches and Executions

Figure 8-2. Single-cycle ALU Operation (Example: INC R0)

AT89LP213/214

**Figure 8-3.** Two-cycle ALU Operation (Example: ADD A, #data)

# 8.1 **Restrictions on Certain Instructions**

The AT89LP213/214 is an economical and cost-effective member of Atmel's growing family of microcontrollers. It contains 2K bytes of Flash program memory. It is fully compatible with the MCS-51 architecture, and can be programmed using the MCS-51 instruction set. However, there are a few considerations one must keep in mind when utilizing certain instructions to program this device. All the instructions related to jumping or branching should be restricted such that the destination address falls within the physical program memory space of the device, which is 2K for the AT89LP213/214. This should be the responsibility of the software programmer. For example, LJMP 7E0H would be a valid instruction, whereas LJMP 900H would not.

#### 8.1.1 Branching Instructions

The LCALL, LJMP, ACALL, AJMP, SJMP, and JMP @A+DPTR unconditional branching instructions will execute correctly as long as the programmer keeps in mind that the destination branching address must fall within the physical boundaries of the program memory size (locations 000H to 7FFH for the AT89LP213/214). Violating the physical space limits may cause unknown program behavior. With the CJNE [...], DJNZ [...], JB, JNB, JC, JNC, JBC, JZ, and JNZ conditional branching instructions, the same previous rule applies. Again, violating the memory boundaries may cause erratic execution. For applications involving interrupts the normal interrupt service routine address locations of the 8051 family architecture have been preserved.

#### 8.1.2 MOVX-related Instructions, Data Memory

The AT89LP213/214 contains 128 bytes of internal data memory. RAM accesses to addresses above 7FH will return invalid data. Furthermore, the stack depth is limited to 128 bytes, the amount of available RAM. The Stack Pointer should not be allowed to point to locations above 7FH. External DATA memory access is not supported in this device, nor is external PROGRAM memory execution. Therefore, no MOVX [...] instructions should be included in the program.

A typical 8051 assembler will still assemble instructions, even if they are written in violation of the restrictions mentioned above. It is the responsibility of the user to know the physical features and limitations of the device being used and to adjust the instructions used accordingly.

# 9. System Clock

The system clock is generated directly from one of three selectable clock sources. The three sources are the on-chip crystal oscillator, external clock source, and internal RC oscillator. The clock source is selected by the Clock Source User Fuses as shown in Table 9-1. No internal clock division is used to generate the CPU clock from the system clock. See "User Configuration Fuses" on page 72.

| Clock Source<br>Fuse 1 | Clock Source<br>Fuse 0 | Selected Clock Source        |

|------------------------|------------------------|------------------------------|

| 0                      | 0                      | Crystal Oscillator           |

| 0                      | 1                      | Reserved                     |

| 1                      | 0                      | External Clock on XTAL1      |

| 1                      | 1                      | Internal 8 MHz RC Oscillator |

#### Table 9-1. Clock Source Settings

### 9.1 Crystal Oscillator

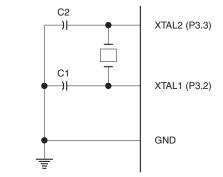

When enabled, the internal inverting oscillator amplifier is connected between XTAL1 and XTAL2 for connection to an external quartz crystal or ceramic resonator as shown in Figure 9-1. Note that in some cases, external capacitors C1 and C2 may **NOT** be required due to the onchip capacitance of the XTAL1 and XTAL2 inputs (approximately 10 pF each). When using the crystal oscillator, P3.2 and P3.3 will have their inputs and outputs disabled. When using the crystal oscillator, XTAL2 should not be used to drive a board-level clock without a buffer.

#### Figure 9-1. Crystal Oscillator Connections

Note: 1. C1, C2 = 5 pF  $\pm$ 5pF for Crystals = 5 pF  $\pm$ 5pF for Ceramic Resonators

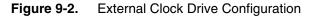

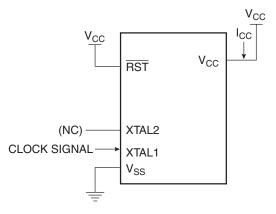

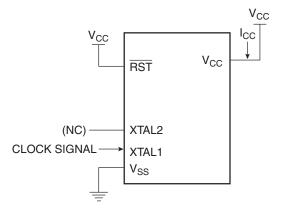

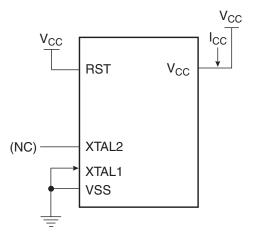

# 9.2 External Clock Source

The external clock option disables the oscillator amplifier and allows XTAL1 to be driven directly by the clock source as shown in Figure 9-2. XTAL2 may be left unconnected, used as P3.3 I/O, or configured to output a divided version of the system clock.

# 9.3 Internal RC Oscillator

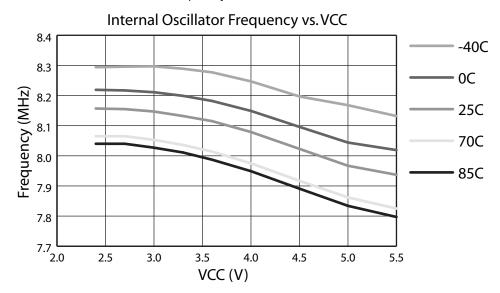

The AT89LP213/214 has an internal RC oscillator tuned to 8.0 MHz  $\pm$ 1.0% at 5.0V and 25°C. When enabled as the clock source, XTAL1 and XTAL2 may be used as P3.2 and P3.3 respectively. XTAL2 may also be configured to output a divided version of the system clock. The frequency of the oscillator may be adjusted by changing the RC Adjust Fuses. (See "User Configuration Fuses" on page 72). A copy of the initial factory setting is stored at location 0007h of the Atmel SIgnature.

# 9.4 System Clock Out

When the AT89LP213/214 is configured to use either an external clock or the internal RC oscillator, a divided version of the system clock may be output on XTAL2 (P3.3). The Clock Out feature is enabled by setting the COE bit in CLKREG. The two CDV bits determine the clock divide ratio. For example, setting COE = "1" and CDIV = "00" when using the internal oscillator will result in a 4.0 MHz clock output on P3.3. P3.3 must be configured as an output in order to use the clock out feature.

#### Table 9-2. CLKREG – Clock Control Register

| CLKRE               | CLKREG = 8FH Reset Value = 0000 0000B |      |      |      |   |      |      |     |  |  |

|---------------------|---------------------------------------|------|------|------|---|------|------|-----|--|--|

| Not Bit Addressable |                                       |      |      |      |   |      |      |     |  |  |

|                     | TPS3                                  | TPS2 | TPS1 | TPS0 | _ | CDV1 | CDV0 | COE |  |  |

| Bit                 | 7                                     | 6    | 5    | 4    | 3 | 2    | 1    | 0   |  |  |

| Symbol                       | Function              | n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                            |  |  |  |  |  |  |

|------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| TPS3<br>TPS2<br>TPS1<br>TPS0 | is implen<br>TPS bits | Timer Prescaler. The Timer Prescaler selects the time base for Timer 0, Timer 1 and the Watchdog Timer. The prescaler is implemented as a 4-bit binary down counter. When the counter reaches zero it is reloaded with the value stored in the TPS bits to give a division ratio between 1 and 16. By default the timers will count every clock cycles (TPS = 0000B). To configure the timers to count at a standard 8051 rate of once every 12 clock cycles, TPS should be set to 1011B. |                                                                                                                                            |  |  |  |  |  |  |

|                              | Clock Ou              | ut Division. [                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Determines the frequency of the clock output relative to the system clock.                                                                 |  |  |  |  |  |  |

|                              | CDIV1                 | <u>CDIV0</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Clock Out Frequency                                                                                                                        |  |  |  |  |  |  |

| CDV1                         | 0                     | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | f/2                                                                                                                                        |  |  |  |  |  |  |

| CDV0                         | 0                     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | f/4                                                                                                                                        |  |  |  |  |  |  |

|                              | 1                     | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | f/8                                                                                                                                        |  |  |  |  |  |  |

|                              | 1                     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | f/16                                                                                                                                       |  |  |  |  |  |  |

| COE                          |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | et COE to output a divided version of the system clock on XTAL2 (P3.3). The internal RC oscillator increases in order to use this feature. |  |  |  |  |  |  |

# 10. Reset

During reset, all I/O Registers are set to their initial values, the port pins are tristated, and the program starts execution from the Reset Vector, 0000H. The AT89LP213/214 has five sources of reset: power-on reset, brown-out reset, external reset, watchdog reset, and software reset.

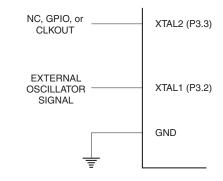

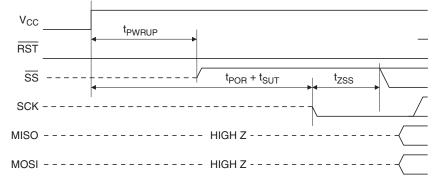

#### 10.1 Power-on Reset

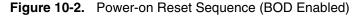

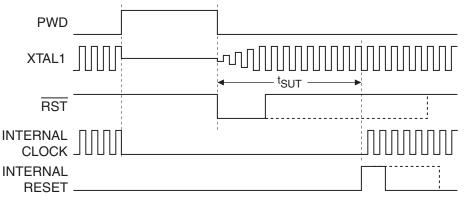

A Power-on Reset (POR) is generated by an on-chip detection circuit. The detection level is nominally 1.4V. The POR is activated whenever  $V_{CC}$  is below the detection level. The POR circuit can be used to trigger the start-up reset or to detect a supply voltage failure in devices without a brown-out detector. The POR circuit ensures that the device is reset from power-on. A power-on sequence is shown in Figure 10-1 on page 15. When  $V_{CC}$  reaches the Power-on Reset threshold voltage  $V_{POR}$ , an initialization sequence lasting  $t_{POR}$  is started. When the initialization sequence completes, the start-up timer determines how long the device is kept in POR after  $V_{CC}$  rise. The POR signal is activated again, without any delay, when  $V_{CC}$  falls below the POR threshold level. A Power-on Reset (i.e. a cold reset) will set the POF flag in PCON. The internally generated reset can be extended beyond the power-on period by holding the RST pin low longer than the time-out.

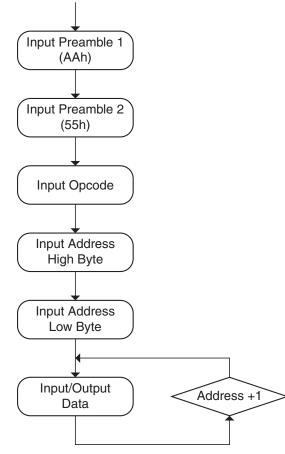

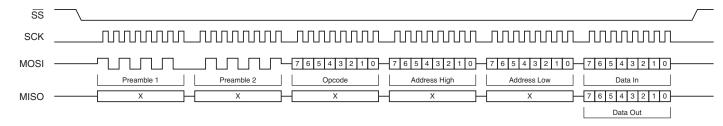

Figure 10-1. Power-on Reset Sequence (BOD Disabled)

If the Brown-out Detector (BOD) is also enabled, the start-up timer does not begin counting until after  $V_{CC}$  reaches the BOD threshold voltage  $V_{BOD}$  as shown in Figure 10-2. However, if this event occurs prior to the end of the initialization sequence, the timer must first wait for that sequence to complete before counting.

Note:  $t_{POR}$  is approximately 92 µs ± 5%.

The start-up timer delay is user configurable with the Start-up Time User Fuses and depends on the clock source (Table 10-1). The start-up delay should be selected to provide enough settling time for  $V_{CC}$  and the selected clock source. The Start-Up Time fuses also control the length of the start-up time after a Brown-out Reset or when waking up from Power-down during internally timed mode.

| SUT Fuse 1 | SUT Fuse 0 | Clock Source               | t <sub>SUT</sub> (± 5%)                                                                                                                                                                  |

|------------|------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0          | 0          | Internal RC/External Clock | 16 µs                                                                                                                                                                                    |

| 0          | 0          | Crystal Oscillator         | 1024 µs                                                                                                                                                                                  |

| 0          | _          | Internal RC/External Clock | 512 µs                                                                                                                                                                                   |

| 0          | 1          | Crystal Oscillator         | 2048 µs                                                                                                                                                                                  |

|            | 2          | Internal RC/External Clock | 1024 µs                                                                                                                                                                                  |

| 1          | 0          | Crystal Oscillator         | Clock         16 μs           1024 μs         1024 μs           Clock         512 μs           2048 μs         2048 μs           Clock         1024 μs           4096 μs         4096 μs |

|            | _          | Internal RC/External Clock | 4096 µs                                                                                                                                                                                  |

|            | 1          | Crystal Oscillator         | 16384 µs                                                                                                                                                                                 |

**Table 10-1.**Start-up Timer Settings

### 10.2 Brown-out Reset

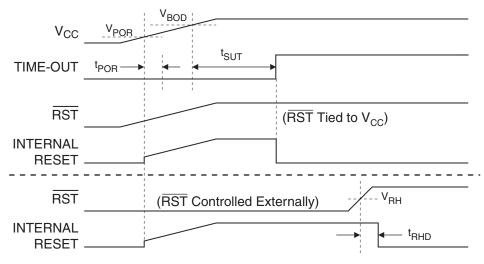

The AT89LP213/214 has an on-chip Brown-out Detection (BOD) circuit for monitoring the  $V_{CC}$  level during operation by comparing it to a fixed trigger level. The trigger level for the BOD is nominally 2.2V. The purpose of the BOD is to ensure that if  $V_{CC}$  fails or dips while executing at speed, the system will gracefully enter reset without the possibility of errors induced by incorrect execution. A BOD sequence is shown in Figure 10-3. When  $V_{CC}$  decreases to a value below the trigger level  $V_{BOD}$ , the internal reset is immediately activated. When  $V_{CC}$  increases above the trigger level, the start-up timer releases the internal reset after the specified time-out period has expired (Table 10-1). The Brown-out Detector must be enabled by setting the BOD Enable Fuse. (See "User Configuration Fuses" on page 72).

# 10.3 External Reset

The P1.3/RST pin can function as either an active-LOW reset input or as a digital general purpose I/O, P1.3. The Reset Pin Enable Fuse, when set to "1", enables the external reset input function on P1.3. (See "User Configuration Fuses" on page 72). When cleared, P1.3 may be used as an input or output pin. When configured as a reset input, the pin must be held low for at least two clock cycles to trigger the internal reset.

Note: During a power-up sequence, the fuse selection is always overridden and therefore the pin will always function as a reset input. An external circuit connected to this pin should not hold this pin LOW during a power-on sequence as this will keep the device in reset until the pin transitions high. After the power-up delay, this input will function either as an external reset input or as a digital input as defined by the fuse bit. Only a power-up reset will temporarily override the selection defined by the reset fuse bit. Other sources of reset will not override the reset fuse bit. P1.3/RST also serves as the In-System Programming (ISP) enable. ISP is enabled when the external reset pin is held low. When the reset pin is disabled by the fuse, ISP may only be entered by pulling P1.3 low during power-up.

### 10.4 Watchdog Reset

When the Watchdog times out, it will generate an internal reset pulse lasting 16 clock cycles. Watchdog reset will also set the WDTOVF flag in WDTCON. To prevent a Watchdog reset, the watchdog reset sequence 1EH/E1H must be written to WDTRST before the Watchdog times out. See "Programmable Watchdog Timer" on page 58 for details on the operation of the Watchdog.

### 10.5 Software Reset

The CPU may generate an internal 16-clock cycle reset pulse by writing the software reset sequence 5AH/A5H to the WDRST register. A software reset will set the SWRST bit in WDT-CON. See "Software Reset" on page 59 for more information on software reset.

# 11. Power Saving Modes

The AT89LP213/214 supports two different power-reducing modes: Idle and Power-down. These modes are accessed through the PCON register.

### 11.1 Idle Mode

Setting the IDL bit in PCON enters idle mode. Idle mode halts the internal CPU clock. The CPU state is preserved in its entirety, including the RAM, stack pointer, program counter, program status word, and accumulator. The Port pins hold the logic states they had at the time that Idle was activated. Idle mode leaves the peripherals running in order to allow them to wake up the CPU when an interrupt is generated. The timers, UART, SPI, and GPI blocks continue to function during Idle. The comparator and watchdog may be selectively enabled or disabled during Idle. Any enabled interrupt source or reset may terminate Idle mode. When exiting Idle mode with an interrupt, the interrupt will immediately be serviced, and following RETI the next instruction to be executed will be the one following the instruction that put the device into Idle.

#### 11.2 Power-down Mode

Setting the Power-down (PD) bit in PCON enters Power-down mode. Power-down mode stops the oscillator, disables the BOD and powers down the Flash memory in order to minimize power consumption. Only the power-on circuitry will continue to draw power during Power-down. During Power-down, the power supply voltage may be reduced to the RAM keep-alive voltage. The RAM contents will be retained, but the SFR contents are not guaranteed once  $V_{CC}$  has been reduced. Power-down may be exited by external reset, power-on reset, or certain interrupts.

#### 11.2.1 Interrupt Recovery from Power-down

Three external interrupts may be configured to terminate Power-down mode. XTAL1 or XTAL2, when not used for the crystal oscillator or external clock, may be used to exit Power-down through external interrupts INT0 (P3.2) and INT1 (P3.3). To wake up by external interrupt INT0 or INT1, that interrupt must be enabled and configured for level-sensitive operation. General purpose interrupt 3 (GPI3) can also wake up the device when the RST pin is disabled. GPI3 must be enabled and configured for low level detection in order to terminate Power-down.

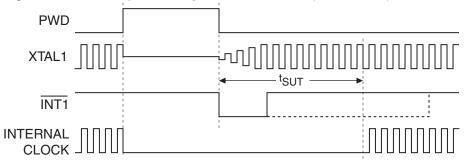

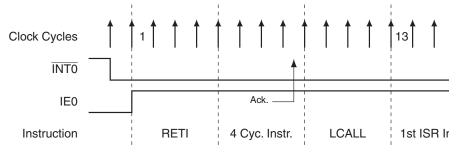

When terminating Power-down by an interrupt, two different wake-up modes are available. When PWDEX in PCON is zero, the wake-up period is internally timed as shown in Figure 11-1. At the falling edge on the interrupt pin, Power-down is exited, the oscillator is restarted, and an internal timer begins counting. The internal clock will not be allowed to propagate to the CPU until after the timer has timed out. After the time-out period the interrupt service routine will

begin. The time-out period is controlled by the Start-up Timer Fuses (see Table 10-1 on page 16). The interrupt pin need not remain low for the entire time-out period.

**Figure 11-1.** Interrupt Recovery from Power-down (PWDEX = 0)

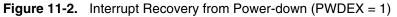

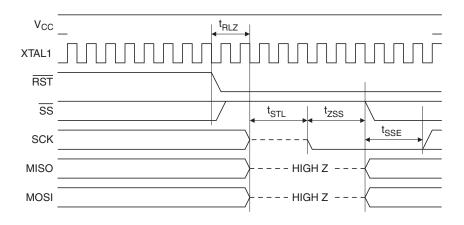

When PWDEX = "1", the wake-up period is controlled externally by the interrupt. Again, at the falling edge on the interrupt pin, power-down is exited and the oscillator is restarted. However, the internal clock will not propagate until the rising edge of the interrupt pin as shown in Figure 11-2. The interrupt pin should be held low long enough for the selected clock source to stabilize. After the rising edge on the pin the interrupt service routine will be executed.

#### 11.2.2 Reset Recovery from Power-down

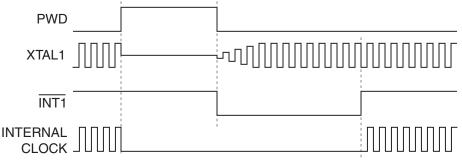

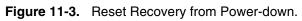

The wake-up from Power-down through an external reset is similar to the interrupt with PWDEX = "0". At the falling edge of RST, Power-down is exited, the oscillator is restarted, and an internal timer begins counting as shown in Figure 11-3. The internal clock will not be allowed to propagate to the CPU until after the timer has timed out. The time-out period is controlled by the Start-up Timer Fuses. (See Table 10-1 on page 16). If RST returns high before the time-out, a two clock cycle internal reset is generated when the internal clock restarts. Otherwise the device will remain in reset until RST is brought high.

| Table 11-1. | PCON – Power Control Register |

|-------------|-------------------------------|

|-------------|-------------------------------|

| PCON     | PCON = 87H Reset Value = 000X 0000B  |                                                                                                                                                                 |                                     |                |                    |                  |                |                |       |  |  |

|----------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|----------------|--------------------|------------------|----------------|----------------|-------|--|--|

| Not Bit  | Addressable                          |                                                                                                                                                                 |                                     |                |                    |                  |                |                |       |  |  |

|          | SMOD1 SMOD0 PWDEX POF GF1 GF0 PD IDL |                                                                                                                                                                 |                                     |                |                    |                  |                |                |       |  |  |

| Bit      | 7                                    | 6                                                                                                                                                               | 5                                   | 4              | 3                  | 2                | 1              | 0              |       |  |  |

| Symbol   | Function                             |                                                                                                                                                                 |                                     |                |                    |                  |                |                |       |  |  |

| SMOD1    | Double Baud                          | I Rate bit. Doul                                                                                                                                                | oles the baud ra                    | ate of the UAF | RT in Modes 1,     | 2, or 3.         |                |                |       |  |  |

| SMOD0    |                                      | Frame Error Select. When SMOD0 = 1, SCON.7 is SM0. When SMOD0 = 1, SCON.7 is FE. Note that FE will be set after a frame error regardless of the state of SMOD0. |                                     |                |                    |                  |                |                |       |  |  |

| PWDEX    |                                      | Exit Mode. Wh<br>er-down is inte                                                                                                                                |                                     | , wake up fror | n Power-down       | is externally co | ntrolled. Wher | PWDEX = 1,     | wake  |  |  |

| POF      |                                      | •                                                                                                                                                               | to "1" during po<br>e. warm resets) | • •            | old reset). It car | n be set or rese | t under softwa | re control and | is no |  |  |

| GF1, GF0 | General-purp                         | oose Flags                                                                                                                                                      |                                     |                |                    |                  |                |                |       |  |  |

| PD       | Power-down                           | bit. Setting this                                                                                                                                               | s bit activates p                   | ower-down op   | peration.          |                  |                |                |       |  |  |

| IDL      | Idle Mode bit                        | t. Setting this b                                                                                                                                               | it activates Idle                   | mode operati   | ion                |                  |                |                |       |  |  |

# 12. Interrupts

The AT89LP213/214 provides 7 interrupt sources: two external interrupts, two timer interrupts, a serial port interrupt, a general-purpose interrupt, and an analog comparator interrupt. These interrupts and the system reset each have a separate program vector at the start of the program memory space. Each interrupt source can be individually enabled or disabled by setting or clearing a bit in the interrupt enable register IE. The IE register also contains a global disable bit, EA, which disables all interrupts.

Each interrupt source (**except** the analog comparator) can be individually programmed to one of four priority levels by setting or clearing bits in the interrupt priority registers IP and IPH. The analog comparator is fixed at the lowest priority level. An interrupt service routine in progress can be interrupted by a higher priority interrupt, but not by another interrupt of the same or lower priority. The highest priority interrupt cannot be interrupted by any other interrupt source. If two requests of different priority levels are pending at the end of an instruction, the request of higher priority level is serviced. If requests of the same priority level are pending at the end of an

instruction, an internal polling sequence determines which request is serviced. The polling sequence is based on the vector address; an interrupt with a lower vector address has higher priority than an interrupt with a higher vector address. Note that the polling sequence is only used to resolve pending requests of the same priority level.

The External Interrupts INT0 and INT1 can each be either level-activated or edge-activated, depending on bits IT0 and IT1 in Register TCON. The flags that actually generate these interrupts are the IE0 and IE1 bits in TCON. When the service routine is vectored to, hardware clears the flag that generated an external interrupt only if the interrupt was edge-activated. If the interrupt was level activated, then the external requesting source (rather than the on-chip hardware) controls the request flag.

The Timer 0 and Timer 1 Interrupts are generated by TF0 and TF1, which are set by a rollover in their respective Timer/Counter registers (except for Timer 0 in Mode 3). When a timer interrupt is generated, the on-chip hardware clears the flag that generated it when the service routine is vectored to.

The Serial Port Interrupt is generated by the logic OR of RI and TI in SCON plus SPIF in SPSR. None of these flags is cleared by hardware when the service routine is vectored to. In fact, the service routine normally must determine whether RI, TI, or SPIF generated the interrupt, and the bit must be cleared by software.

A logic OR of all eight flags in the GPIF register causes the general-purpose interrupt. None of these flags is cleared by hardware when the service routine is vectored to. The service routine must determine which bit generated the interrupt, and the bit must be cleared in software. If the interrupt was level activated, then the external requesting source must de-assert the interrupt before the flag may be cleared by software.

The CF bit in ACSR generates the Comparator Interrupt. The flag is not cleared by hardware when the service routine is vectored to and must be cleared by software.

Most of the bits that generate interrupts can be set or cleared by software, with the same result as though they had been set or cleared by hardware. That is, interrupts can be generated and pending interrupts can be canceled in software. The two exceptions are the SPI interrupt flag SPIF and the general-purpose interrupt flags in GPIF. These flags are only set by hardware and may only be cleared by software.

| Interrupt                 | Source            | Vector Address |

|---------------------------|-------------------|----------------|

| System Reset              | RST or POR or BOD | 0000H          |

| External Interrupt 0      | IEO               | 0003H          |

| Timer 0 Overflow          | TF0               | 000BH          |

| External Interrupt 1      | IE1               | 0013H          |

| Timer 1 Overflow          | TF1               | 001BH          |

| Serial Port               | RI or TI or SPIF  | 0023H          |

| General-purpose Interrupt | GPIF              | 002BH          |

| Analog Comparator         | CF                | 0033H          |

Table 12-1. Interrupt Vector Addresses

### 12.1 Interrupt Response Time

The interrupt flags may be set by their hardware in any clock cycle. The interrupt controller polls the flags in the last clock cycle of the instruction in progress. If one of the flags was set in the preceding cycle, the polling cycle will find it and the interrupt system will generate an LCALL to the appropriate service routine as the next instruction, provided that the interrupt is not blocked by any of the following conditions: an interrupt of equal or higher priority level is already in progress; the instruction in progress is RETI or any write to the IE, IP, or IPH registers. Either of these condition ensures that if the instruction in progress is RETI or any access to IE, IP or IPH, then at least one more instruction will be executed before any interrupt is vectored to. The polling cycle is repeated at the last cycle of each instruction, and the values polled are the values that were present at the previous clock cycle. If an active interrupt flag is not being serviced because of one of the above conditions and is no longer active when the blocking condition is removed, the denied interrupt will not be serviced. In other words, the fact that the interrupt flag was once active but not serviced is not remembered. Every polling cycle is new.

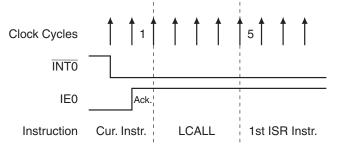

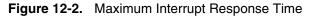

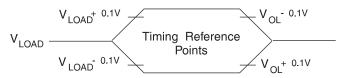

If a request is active and conditions are met for it to be acknowledged, a hardware subroutine call to the requested service routine will be the next instruction executed. The call itself takes four cycles. Thus, a minimum of five complete clock cycles elapsed between activation of an interrupt request and the beginning of execution of the first instruction of the service routine. A longer response time results if the request is blocked by one of the previously listed conditions. If an interrupt of equal or higher priority level is already in progress, the additional wait time depends on the nature of the other interrupt's service routine. If the instruction in progress is not in its final clock cycle, the additional wait time cannot be more than 3 cycles, since the longest are only 4 cycles long. If the instruction in progress is RETI or an access to IE or IP, the additional wait time cannot be more than 7 cycles (a maximum of three more cycles to complete the instruction in progress, plus a maximum of 4 cycles to complete the next instruction). Thus, in a single-interrupt system, the response time is always more than 5 clock cycles and less than 13 clock cycles. See Figures 12-1 and 12-2.

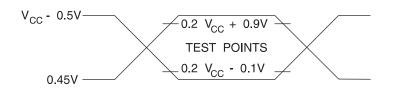

#### Figure 12-1. Minimum Interrupt Response Time

# Table 12-2. IE – Interrupt Enable Register

| IE = A8 | E = A8H Reset Value = 0000 0000B                                                                                                                                |                 |        |    |     |     |     |     |  |  |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------|----|-----|-----|-----|-----|--|--|

| Bit Add | Bit Addressable                                                                                                                                                 |                 |        |    |     |     |     |     |  |  |

|         | EA                                                                                                                                                              | EC              | EGP    | ES | ET1 | EX1 | ET0 | EX0 |  |  |

| Bit     | 7                                                                                                                                                               | 6               | 5      | 4  | 3   | 2   | 1   | 0   |  |  |

| Symbol  | Function                                                                                                                                                        |                 |        |    |     |     |     |     |  |  |

| EA      | Global enable/disable. All interrupts are disabled when EA = 0. When EA = 1, each interrupt source is enabled/disabled by setting /clearing its own enable bit. |                 |        |    |     |     |     |     |  |  |

| EC      | Comparator I                                                                                                                                                    | nterrupt Enabl  | е      |    |     |     |     |     |  |  |

| EGP     | General-purp                                                                                                                                                    | ose Interrupt I | Enable |    |     |     |     |     |  |  |

| ES      | Serial Port In                                                                                                                                                  | terrupt Enable  |        |    |     |     |     |     |  |  |

| ET1     | Timer 1 Inter                                                                                                                                                   | rupt Enable     |        |    |     |     |     |     |  |  |

| EX1     | External Inte                                                                                                                                                   | rrupt 1 Enable  |        |    |     |     |     |     |  |  |

| ET0     | Timer 0 Inter                                                                                                                                                   | rupt Enable     |        |    |     |     |     |     |  |  |

| EX0     | External Inte                                                                                                                                                   | rrupt 0 Enable  |        |    |     |     |     |     |  |  |

# Table 12-3. IP – Interrupt Priority Register

Timer 1 Interrupt Priority Low

Timer 0 Interrupt Priority Low

External Interrupt 1 Priority Low

External Interrupt 0 Priority Low

PT1

PX1

PT0

PX0

| IP = B | 8H Reset Value = X000 0000B            |   |     |    |     |     |     |     |  |

|--------|----------------------------------------|---|-----|----|-----|-----|-----|-----|--|

| Bit Ad | dressable                              |   |     |    |     |     |     |     |  |

|        | _                                      | - | PGP | PS | PT1 | PX1 | PT0 | PX0 |  |

| Bit    | 7                                      | 6 | 5   | 4  | 3   | 2   | 1   | 0   |  |

| Symbol | Function                               |   |     |    |     |     |     |     |  |

| PGP    | General-purpose Interrupt Priority Low |   |     |    |     |     |     |     |  |

| PS     | Serial Port Interrupt Priority Low     |   |     |    |     |     |     |     |  |

#### Table 12-4. IPH – Interrupt Priority High Register

| IPH =  | IPH = B7H Reset Value = X000 00         |                                 |        |     |      |      |      |      |

|--------|-----------------------------------------|---------------------------------|--------|-----|------|------|------|------|

| Not Bi | t Addressable                           |                                 |        |     |      |      |      |      |

|        | -                                       | _                               | PGH    | PSH | PT1H | PX1H | PT0H | PX0H |

| Bit    | 7                                       | 6                               | 5      | 4   | 3    | 2    | 1    | 0    |

| Symbol | Function                                |                                 |        |     |      |      |      |      |

| PGH    | General-purpose Interrupt Priority High |                                 |        |     |      |      |      |      |

| PSH    | Serial Port Ir                          | nterrupt Priority               | / High |     |      |      |      |      |

| PT1H   | Timer 1 Inter                           | Timer 1 Interrupt Priority High |        |     |      |      |      |      |

| PX1H   | External Interrupt 1 Priority High      |                                 |        |     |      |      |      |      |

| PT0H   | Timer 0 Interrupt Priority High         |                                 |        |     |      |      |      |      |

| PX0H   | External Interrupt 0 Priority High      |                                 |        |     |      |      |      |      |

# 13. I/O Ports

The AT89LP213/214 can be configured for between 9 and 12 I/O pins. The exact number of I/O pins available depends on the clock and reset options as shown in Table 13-1. All port pins are 5V tolerant as inputs, that is they can be pulled up or driven to 5.5V even when operating at a lower  $V_{CC}$  such as 3V.

| Table 13-1. | I/O Pin Configurations |

|-------------|------------------------|

|-------------|------------------------|

| Clock Source                   | Reset Option      | Number of I/O Pins |

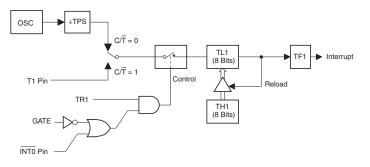

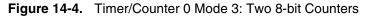

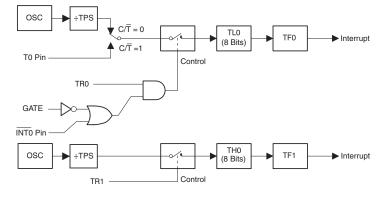

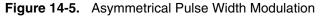

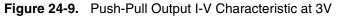

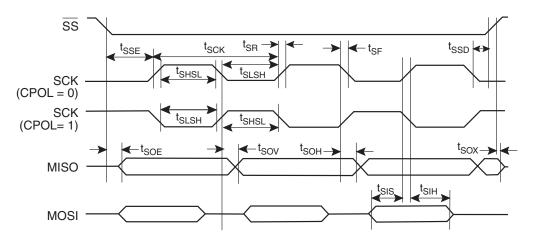

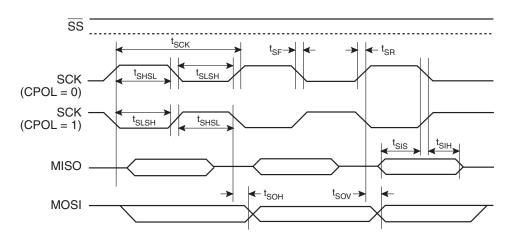

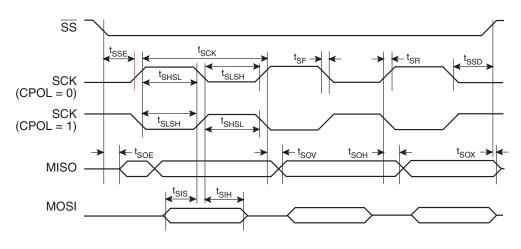

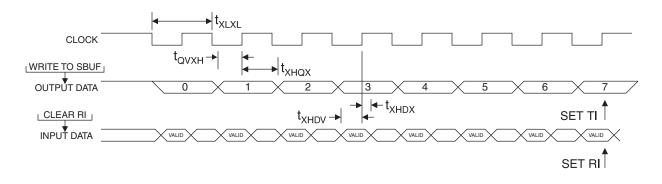

|--------------------------------|-------------------|--------------------|